… Retour à la Présentation du projet

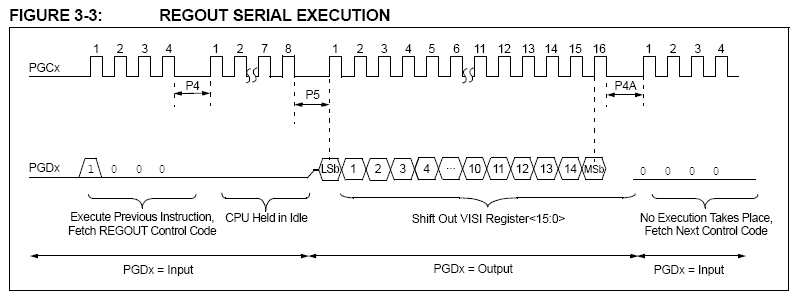

- 2.2.3 – Opération Regout Serial Execution

L’opération REGOUT consiste à sérialiser un 1er train de 4 bits égaux à 0001 correspondant à la commande REGOUT (bit de faible en tête), suivi d’un 2ème train de 8 bits à 0 et puis après le temps P5 (paramètre TDLY2) d’une durée supérieure à 40 nS à désérialiser 16 bits avec le bit de poids faible en tête (little-endian) correspondant à la donnée présentée par le circuit cible au travers du registre VISI (0x784).

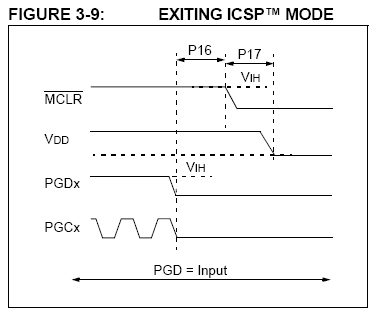

- 2.2.4 – Sortie du mode ICSP™

La sortie du mode ICSP™ est décrite sur la figure ci-contre sur laquelle le temps P17 (paramètre THLD3 du § 7.0 AC/DC CHARACTERISTICS AND TIMING REQUIREMENTS) pendant lequel l’alimentation VDD du circuit est maintenue après la mise au niveau bas de MCLR/ doit être supérieur à 100 nS.

A noter que les 2 lignes PGD et PGC doivent être mises au niveau bas avant ou au plus tard avec celle de la ligne MCLR/ du fait de la durée minimum de P16 – paramètre TDLY10 – qui est spécifiée à une valeur nulle.