- 1a – Bits de configuration pour le système d’horloge

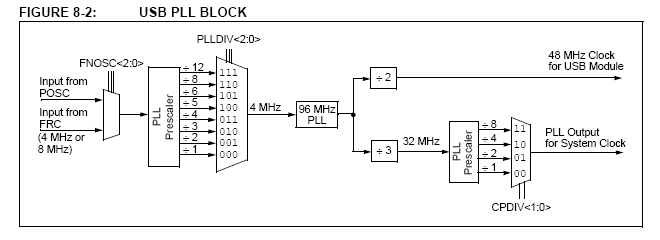

Nous utilisons pour ce programme la source Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL) connectée au quartz externe de 12 MHz pour avoir une fréquence Fosc de 32 MHz permettant l’exécution d’une instruction (hors débranchement, hors accès I/O et hors mécanisme Stall) en 62.5 nS correspondant à Fosc / 2. Pour cela, les bits de configuration suivants doivent être initialisés comme indiqué ci-après (cf. § 8.5 Oscillator Modes and USB Operation – Page 110 du document Spécifications PIC24FJ64GB004 Family avec notamment la FIGURE 8-2 USB PLL BLOCK) :

| Bits | Descriptions => Items choisis |

Valeurs binaires |

| POSCMD<1:0> | Primary Oscillator Configuration bits => HS Oscillator mode selected | 10 |

| FNOSC<2:0> | Initial Oscillator Select bits => Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL) | 011 |

| PLLDIV<2:0> | USB 96 MHz PLL Prescaler Select bits => Oscillator input divided by 3 (12 MHz input) |

010 |

| CPDIV<1:0> | USB System Clock Select bits (postscaler select from 32 MHz clock branch) => 32 MHz (divide by 1) | 00(1) |

| PLL96MHZ | USB 96 MHz PLL Start-up Enable bit => 96 MHz PLL is enabled by user in software (controlled with the PLLEN bit in CLKDIV<5>) |

0 |

Note 1 : Valeurs déterminées par le registre CLKDIV initialisé à 0x0100 au Reset ; toutes les autres valeurs le sont par le registre CW2 qui est initialisé à 0xFFA38E.

- 1b – Les autres bits de configuration

Toutes les définitions des autres bits de configuration sont largement commentées dans le listing du programme auquel il convient d’apporter les précisions suivantes :

- Les bits CW1<GCP>, CW1<GWRP>, CW3<WPEND>, CW3<WPCFG> et CW3<WPDIS> à 1 autorisent d’écrire et de lire les zones programme et les registres de configuration du circuit.

- Le bit CW1<DEBUG> à 1 indique que le mode Debug n’est pas activé.

- Tous les bits relatifs au Watchdog sont positionnés mais ne seront pas utiles dans ce premier programme.